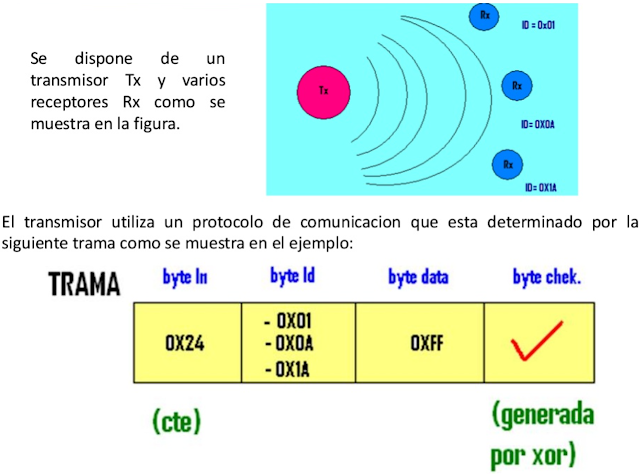

▷ DISEÑO DE UN SISTEMA DIGITAL RECEPTOR DE COMUNICACIÓN SERIAL EN #VHDL CON #FPGA #DE0_NANO

⭐⭐⭐⭐⭐ S. D. RECEPTOR DE COMUNICACIÓN SERIAL EN #VHDL CON #FPGA #DE0_NANO from Victor Asanza ➡️ #DigitalSystems #DigitalElectronic #DigitalCircuits #HDL #VHDL #FPGA ⭐ https://github.com/vasanza/MSI-VHDL ✅ Partición Funcional: ✅ Algorithmic State Machine #ASM: ✅ Código #VHDL: Leer temas relacionados: ✅ 2020 Paper: Behavioral Signal Processing with Machine Learning based on #FPGA ✅ 2020 Paper: Implementation of a Classification System of #EEG Signals Based on #FPGA ✅ 2020 Paper: Monitoring of system memory usage embedded in #FPGA ✅ 2019: Artificial Neural Network based #EMG recognition for gesture communication (#InnovateFPGA) ✅ Projects Digital Systems Design #FPGA ➡️ Example: Determinant of a matrix ➡️ Example: Numeric Sequence Detector ➡️ Example: Efficient Number Sequence Detector ➡️ Example: set operations ➡️ Example: communication and checksum validation ➡️ Example: Sum of Prod...