▷ EyeTracker Classification of subjects with Parkinson's using Machine Learning #ML based on #FPGA

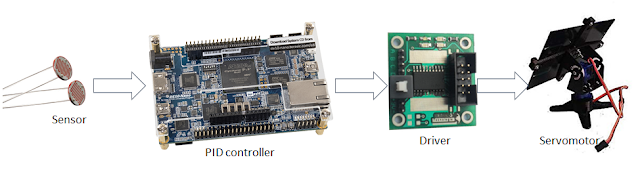

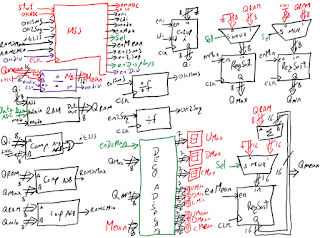

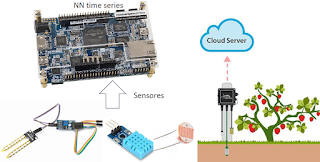

⭐⭐⭐⭐⭐ EyeTracker Classification of subjects with Parkinson's using Machine Learning #ML based on #FPGA ➡️ #DigitalSystems #DigitalElectronic #DigitalCircuits #HDL #VHDL #FPGA ⭐ https://github.com/vasanza/MSI-VHDL 🥇 Publication: Asanza, V., Sánchez-Pozo, N. N., Lorente-Leyva, L. L., Peluffo-Ordóñez, D. H., Loayza, F. R., & Peláez, E. (2021). Classification of Subjects with Parkinson’s Disease using Finger Tapping Dataset. IFAC-PapersOnLine, 54(15), 376-381. ✅ Objectives: Caracterizar las señales EEG y EMG en el dominio del tiempo. Comparar el desempeño de uno o más algoritmos de clasificación. Medir los tiempos de procesamiento, % de CPU utilizado y % de memoria utilizada, en el procesador NIOSII, ARM ó ambos, según sea el caso (radar chart). ✅ Goals: Implementar un Sistema Embebido basado en #FPGA que lea datos preprocesados (.csv o .mat) almacenados en memoria Double Data Rate 3 Synchronous Dynamic Random-Access Memory #DDR3_SDRAM, el ac...