▷ SOLUCIÓN LECCIÓN SISTEMAS DIGITALES 1, 1er Parcial (2021 PAE) C3

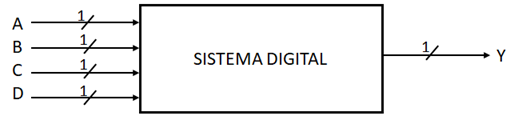

⭐⭐⭐⭐⭐ SOLUCIÓN LECCIÓN SISTEMAS DIGITALES 1, 1er Parcial (2021 PAE) C3 from Victor Asanza ➡️ #DigitalSystems #DigitalElectronic #DigitalCircuits #HDL #VHDL #FPGA ⭐ https://github.com/vasanza/MSI-VHDL El siguiente es un Sistema Digital que tiene las señales ‘A’,’ B’, ‘C’ y ‘D’ como entradas de un bit; por otro lado, la señal ‘Y’ es una salida de un bit tal como se muestra en la siguiente imagen: El comportamiento de la señal de salida ‘Y’ en función de las señales de entrada es la siguiente: Para describir el comportamiento del sistema, se propone utilizar el siguiente código VHDL que está incompleto: Dadas las siguientes opciones, indicar cuál es la correcta asignación de señal para X0, X1, X2 y X3: a) with A&B&C&D select Y<= ‘1’ when “0000”|“0011” |“0101” |“0110”, ‘0’ when others; b) with A&B&C&D select Y<= ‘1’ when “0001”|“0010” |“0100” |“0111”, ‘0’ when others; c) with A&B&C&D select Y<= ‘1’ when “0000”|“0011”...