▷ SISTEMA CONTROLADOR DE PERSONAL DE TRABAJO EN #VHDL CON #FPGA #DE0NANO

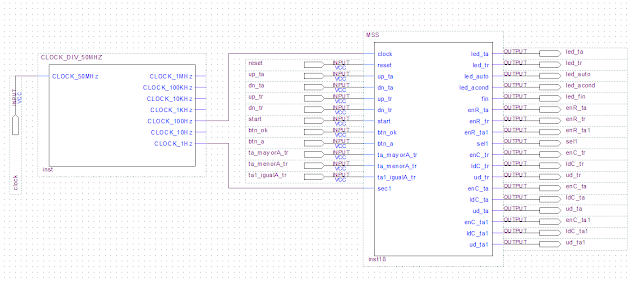

⭐⭐⭐⭐⭐ SISTEMA CONTROLADOR DE PERSONAL DE TRABAJO EN #VHDL CON #FPGA #DE0_NANO ➡️ #DigitalSystems #DigitalElectronic #DigitalCircuits #HDL #VHDL #FPGA ⭐ https://github.com/vasanza/MSI-VHDL ✅ Por: Jorge Luis Ramirez Gomez ( jolurami@espol.edu.ec ) Maria Gracia Constante Sanchez ( mgconsta@espol.edu.ec ) ✅ DESCRIPCIÓN: Realizar el diseño y la implementación de un circuito CONTROLADOR DE PERSONAL DE TRABAJO. El sistema controla el ingreso y salida de forma automática del personal de trabajo (mínimo 3, un botón de ID por cada trabajador). Cuando un trabajador entra o sale debe autentificarse con un ID único para cada persona y además deberá presionar un botón indicando si está ingresando o saliendo de trabajar. El sistema tiene además un pulsador que le sirve para iniciar el sistema (START) y un botón de RESET para inicializarlo todo. Al finalizar la jornada de trabajo, el sistema debe indicar reportes de los tiempos de trabajo de cada persona en dos displays, usando los botones...