▷ SISTEMA DE ACONDICIONAMIENTO DE TEMPERATURA EN #VHDL CON #FPGA #DE0NANO

⭐⭐⭐⭐⭐ SISTEMA DE ACONDICIONAMIENTO DE TEMPERATURA EN #VHDL CON #FPGA #DE0NANO

- ➡️ #DigitalSystems #DigitalElectronic #DigitalCircuits #HDL #VHDL #FPGA

- ⭐ https://github.com/vasanza/MSI-VHDL

✅ Por:

- Stephano Leon Toala (steanleo@espol.edu.ec)

- Niel Mayor Fuentes (nmayor@espol.edu.ec)

✅ DESCRIPCIÓN:

Diseñar una MSS de un sistema ACONDICIONADOR DE TEMPERATURA UTOMATICO. Para dar inicio se debe presionar y soltar el botón de START.

El circuito debe tener dos botoneras para introducir la temperatura actual “medida” de un

laboratorio (UP)/(DOWN), otros dos botones permiten setear la temperatura deseada

(UP)/(DOWN), otro botón le permitirá al sistema activar el modo automático (A).

Una vez presionada la tecla START (ST) el SISTEMA deberá recibir el número de la temperatura

ambiente subiendo o bajando con los dos botones y también deberá recibir el número de la

temperatura deseada (set-point). El botón automático dará la orden para que el sistema compare

las temperaturas. Si la temperatura del laboratorio es menor a la del set-point, el sistema encenderá

el acondicionador incrementando así un grado centígrado por segundo; en caso de que la

temperatura del laboratorio sea mayor a la del set-point el sistema apagará el acondicionador y

por tanto se decrementará un grado centígrado cada dos segundos.

La salida del CONTROLADOR serán: dos Displays para mostrar la temperatura medida en

tiempo real del laboratorio en grados centígrados, dos Displays son para mostrar la temperatura

deseada (set-point), un led para indicar el encendido/apagado del acondicionador de aire. Un led

adicional indicará si el sistema está en modo automático o no.

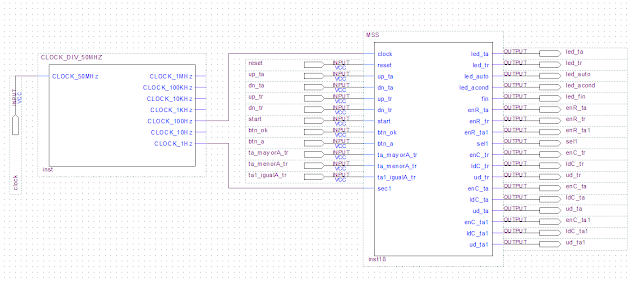

✅ PARTICIÓN FUNCIONAL:

✅ ESQUEMÁTICO #ALTIUM #DESIGNER:

✅ DIAGRAMA #ASM:

✅ DIAGRAMA TIEMPO:

✅ ARCHIVOS #VHDL DROPBOX:

Leer temas relacionados:

- ✅ 2020 Paper: Behavioral Signal Processing with Machine Learning based on #FPGA

- ✅ 2020 Paper: Implementation of a Classification System of #EEG Signals Based on #FPGA

- ✅ 2020 Paper: Monitoring of system memory usage embedded in #FPGA

- ✅ 2019: Artificial Neural Network based #EMG recognition for gesture communication (#InnovateFPGA)

- ✅ Projects Digital Systems Design #FPGA

- ➡️ Example: Determinant of a matrix

- ➡️ Example: Numeric Sequence Detector

- ➡️ Example: Efficient Number Sequence Detector

- ➡️ Example: set operations

- ➡️ Example: communication and checksum validation

- ➡️ Example: Sum of Products Karnaugh Map

- ➡️ Example: Multiplying 3x4 matrix by 4x3 matrix

- ➡️ Example: Consecutive 1's Counter

- ➡️ Example: Numeric Sequence Counter

- ➡️ Example: Serial communication receiver

- ➡️ Example: billing system for telephone booths

- ➡️ Example: Temperature Conditioner

- ➡️ Example: Access control system (2)

- ➡️ Example: Access control system (1)

✅ LINK VIDEO:

Comentarios

Publicar un comentario