▷ Monitoring of system memory usage embedded in #FPGA

- ➡️ #DigitalSystems #DigitalElectronic #DigitalCircuits #HDL #VHDL #FPGA

- ➡️ 2020 International Conference on Applied Electronics (AE)

- ⭐ Read full paper: https://ieeexplore.ieee.org/abstract/document/9232863

- ⭐ Source code repository: https://github.com/VHDL-Digital-Systems

- When using this resource, please cite the original publication:

✅ Conference content:

- Field Programmable Gate Array #FPGA

- System on Chip #SoC

- #Nios_II_Processor

- Hard Processor System #HPS

- Advanced RISC Machine #ARM

- Logical bridges

- Share physical resources

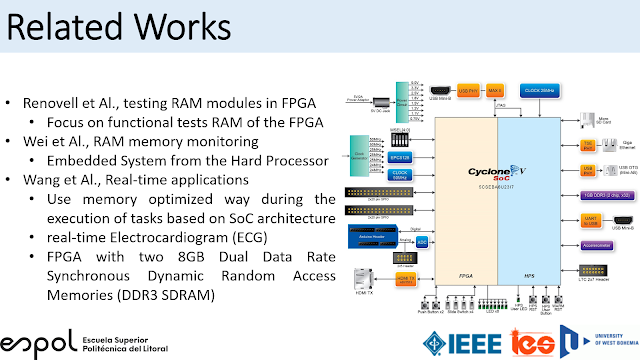

- Related Work:

- Renovell et Al., testing #RAM modules in #FPGA, Focus on functional tests RAM of the FPGA.

- Wei et Al., RAM memory monitoring, Embedded System from the #HardProcessor.

- Wang et Al., Real-time applications, Use memory-optimized way during the execution of tasks based on SoC architecture.

- Real-time Electrocardiogram #ECG

- FPGA with two 8GB Dual Data Rate Synchronous Dynamic Random Access Memories #DDR3 #SDRAM

- Results:

- As shown in Fig 12, the SRAM is working in the logical part executing several tasks and it is validated that as time passes the memory consumption increases. In addition, the writing times will depend on the amount of memory to be written and this varies according to the task that is being executed by the user or those that he has programmed in the Nios II.

- As for the DD3, it is executing the Linux OS as a basis and additionally, a size proportional to the size of the SRAM is reserved for the respective comparisons, so it is observed that it has a higher consumption and longer response times. It should be considered in this comparison that the DD3 in addition to running the OS, also has the web server implemented which consumption varies according to the clients that are connecting to the webpage where it can be seen the memory monitoring of the embedded system. Also, thanks to the part of the HPS it is possible to monitor the memory of the embedded system without affecting its consumption.

- As shown in Fig. 13, the SRAM is not under the same workload since it is only responsible for storing what Nios II needs for the execution of the tasks.

- Finally, it was consider that the HPS portion to be very important for a clean monitoring not only of the SRAM but also of any core that is implemented in the FPGA portion, since if this application is implemented on a chip that only has FPGA the application would affect the consumption and performance of it, therefore you could not have completely reliable results.

✅ References:

- Michael Daum (2017). GSRD v13.1 - Device Tree Generator. [online] RocketBoards.org. Available at: https://rocketboards.org/foswiki/view/Documentation/Device TreeGenerator131 [Accessed 25 Sep. 2019].

- Terasic. (2017). LINUX X64 INSTALLATION. En DE10 Standard Control Panel(14-39). United statess: Terasic.com

- Renovell, M., Portal, J., Figueras, J. et al. SRAM-Based FPGAs: Testing the Embedded RAM Modules (1999) 14: 159. https://doi.org/10.1023/A:1008326111919

- Wei Kang Huang ; F.J. Meyer ; Xiao-Tao Chen ; F. Lombardi, et al. Testing memory modules in SRAM-based configurable FPGAs (1997). https://ieeexplore.ieee.org/abstract/document/619399

- Intel FPGA (2015). Combining a Nios II ELF executable into a Hardware Project SOF file. [video] Available at: https://www.youtube.com/watch?v=joFaxLY-rUE [Accessed 26 Aug. 2019].

- Cyclone V Hard Processor System Technical Reference Manual. (2018). 4th ed. [ebook] San Jose, CA 95134. Available at: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/cyclone-v/cv_54005.pdf [Accessed 26 Jul. 2019].

- Intel.com. (2019). Intel SoC FPGA Embedded Development Suite User Guide. [online] Available at: https://www.intel.com/content/www/us/en/programmable/documentation/lro1402536290550.html [Accessed 26 Jul. 2019].

- Using Linux on the DE1-SoC. (2017). [ebook] Intel Corporation-FPGA University Program. Available at: https://software.intel.com/en-us/fpga-academic [Accessed 26 Jul. 2019].

- Wang, X., Zhu, Y., Ha, Y., Qiu, M., & Huang, T. (2017). An FPGA-based cloud system for massive ECG data analysis. IEEE Transactions on Circuits and Systems II: Express Briefs, 64(3), 309-313.

- C. Cedeño Z., J. Cordova-Garcia, V. Asanza A., R. Ponguillo and L. Muñoz M., "k-NN-Based EMG Recognition for Gestures Communication with Limited Hardware Resources," 2019 IEEE SmartWorld, Ubiquitous Intelligence & Computing, Advanced & Trusted Computing, Scalable Computing & Communications, Cloud & Big Data Computing, Internet of People and Smart City Innovation (SmartWorld/SCALCOM/UIC/ATC/CBDCom/IOP/SCI), Leicester, United Kingdom, 2019, pp. 812-817.

Read related topics:

- ✅ Implementation of a Classification System of #EEG Signals Based on #FPGA

- ✅ Artificial Neural Network based #EMG recognition for gesture communication (#InnovateFPGA)

- ✅ Projects Digital Systems Design #FPGA

- ✅ 2020 PAO1: Proyectos Propuestos

- ✅ End Device #Arduino #FreeRTOS

- ✅ End Device + Coordinator #Raspberry Pi #Python

Comentarios

Publicar un comentario