▷ SOLUCIÓN EVALUACIÓN SISTEMAS DIGITALES 1, 1er Parcial (2021 PAO1)

- ➡️ #DigitalSystems #DigitalElectronic #DigitalCircuits #HDL #VHDL #FPGA

- ⭐ https://github.com/vasanza/MSI-VHDL

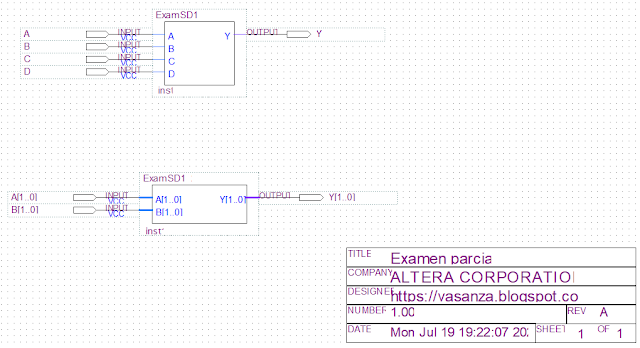

✅ Problema #1 (x%). El siguiente es un Sistema Digital que tiene las señales ‘A’,’ B’, ‘C’ y ‘D’ como entradas de un bit; por otro lado, la señal ‘Y’ es una salida de un bit tal como se muestra en la siguiente imagen:

El comportamiento de la señal de salida ‘Y’ en función de las señales de entrada, es descrito con el siguiente código VHDL:

⭐ Código GitHub:

Realizar los siguientes desarrollos:

a) Usando mapas de karnaught y agrupamiento de minterms (SOP), simplificar la expresión booleana hasta obtener su minima expresión (x/2 %).

b) Utilizando puertas lógicas, graficar el circuito que represente a la ecuación simplificada en el literal anterior (x/2 %).

b)

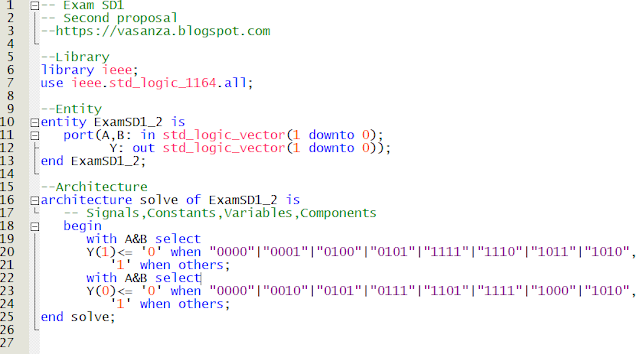

✅ Problema #2 (x%). El siguiente es un Sistema Digital que tiene las señales ‘A’ y ‘B’ como entradas de dos bits; por otro lado, la señal ‘Y’ es una salida de dos bits tal como se muestra en la siguiente imagen:

El comportamiento de la señal de salida ‘Y’ en función de las señales de entrada, es descrito con el siguiente código VHDL:

⭐ Código GitHub:

Realizar los siguientes desarrollos:

a) Usando mapas de karnaught y agrupamiento de minterms (SOP), simplificar la expresión booleana hasta obtener su minima expresión de Y(1) = f(A(1),A(0),B(1),B(0)) y Y(0) = f(A(1),A(0),B(1),B(0)) (x/2 %).

b) Indicar con sus propias palabras el funcioamiento que realiza el sistemas digital propuesto (x/2 %).

Resolución:

a)

b) Es una puerta XOR de dos entradas de dos bits y una salida de dos bits.

Read related topics

- ⭐ https://github.com/vasanza/MSI_VHDL

- ✅ Video de #VHDL (Ejemplo 2 - secuencialidad)

- ✅ Video de #VHDL (Ejemplo 1 - concurrencia)

- ✅ 2021 PAO1: 1ra Lección C2

- ✅ 2021 PAO1: 1ra Lección C1

- ✅ 2021 PAE: Examen 1ra Evaluación

- ✅ 2021 PAE: 1ra Lección C2

- ✅ 2021 PAE: 1ra Lección C1

- ✅ 2020 PAO1: Examen 1ra Evaluación

- ✅ 2020 PAO1: 1ra Lección C1-3 B

- ✅ 2020 PAO1: 1ra Lección C1-3A

- ✅ 2018 1T: Examen 1ra Evaluación

- ✅ 2017 2T: Lección 2da Evaluación

- ✅ 2017 2T: Lección 1ra Evaluación

- ✅ 2017 1T: Lección 2da Evaluación

- ✅ 2017 1T: Examen 1ra Evaluación

- ✅ 2017 1T: Lección 1ra Evaluación

- ✅ 2017 1T: Ejercicios 1ra Evaluación

Comentarios

Publicar un comentario