▷ SOLUCIÓN EVALUACIÓN SISTEMAS DIGITALES 1, 1er Parcial (2021 PAE)

- ➡️ #DigitalSystems #DigitalElectronic #DigitalCircuits #HDL #VHDL #FPGA

- ⭐ https://github.com/vasanza/MSI-VHDL

✅ Problema #1 (30%). Se desea diseñar un Sistemas Digital que capaz de controlar dos actuadores tipo bomba (A y B) en función del nivel de agua presente en un tanque. Este nivel de agua se monitorea con dos sensores (S0 y S1). El Sistemas Digital se muestra en la siguiente gráfica:

El funcionamiento del sistema digital se detalla a continuación:

• El caudal de entrada de agua se abre (A=1) o se cierra (A=0) con el ánimo de controlar el nivel del agua presente en el tanque. Si el nivel del agua es el Mínimo (S1 = 0 y S0 = 1) o menor al mínimo (S1=0 y S0=0) entonces el actuador tipo bomba (A) debe ser abierto (A = 1); por otro lado, si el nivel del agua es el Máximo (S1 = 1 y S0 = 1) entonces el actuador tipo bomba (A) debe ser cerrado (A = 0).

• El caudal de salida debe estar abierto (B=1) siempre y cuando el tanque de agua tenga un nivel de agua entre el máximo y el mínimo (S1 =0 y S0 =1) o (S1 =1 y S0 =1). En caso de tener un nivel de agua menor al mínimo (S1 =0 y S0 =0), entonces el caudal de salida debe estar cerrado (B=0).

• Recuerde que no es posible que el sensor de nivel máximo (S1) esté detectando agua mientras que el sensor de nivel mínimo (S0) no la detecta (S1=1 y S0=0)

Realizar los siguientes desarrollos:

a) Completar la siguiente Tabla de Verdad

b) Utilizando mapas de Karnaugh obtener la expresión booleana minimizada de las salidas A y B

c) Utilizando puertas nand de dos entradas hacer el circuito resultante de las salidas A y B

✅ Problema #2 (30%). El siguiente es un Sistema Digital que tiene las señales ‘A’,’ B’, ‘C’ y ‘D’ como entradas de un bit; por otro lado, la señal ‘Y’ es una salida de un bit tal como se muestra en la siguiente imagen:

El comportamiento de la señal de salida ‘Y’ en función de las señales de entrada, es descrito con el siguiente código VHDL:

Realizar los siguientes desarrollos:

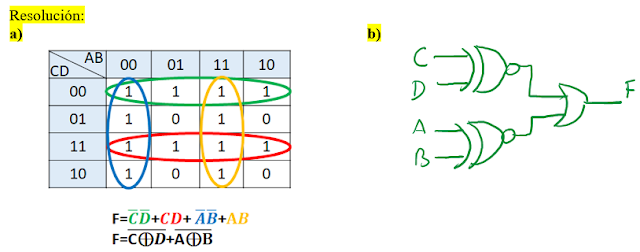

a) Usando mapas de karnaught y agrupamiento de minterms, simplicar la expresión booleana al mínimo.

b) Utilizando puertas lógicas, graficar el circuito que represente a la ecuación simplificada en el literal anterior.

✅ Problema #3 (20%). El siguiente es un Sistema Digital que tiene las señales ‘A’,’ B’, ‘C’ y ‘D’ como entradas de un bit; por otro lado, la señal ‘Y’ es una salida de un bit tal como se muestra en la siguiente imagen:

Para describir el comportamiento del sistema, se propone utilizar el siguiente código VHDL que está incompleto:

Dadas las siguientes opciones, indicar cuál es la correcta asignación de señal para X0, X1, X2 y X3:

a) with A&B&C&D select Y<= ‘1’ when “1100”|“1111” |“1001” |“1010”, ‘0’ when others;

b) with A&B&C&D select Y<= ‘1’ when “1101”|“1110” |“1000” |“1011”, ‘0’ when others;

c) with A&B&C&D select Y<= ‘1’ when “0000”|“0011” |“1100” |“1111”, ‘0’ when others;

d) with A&B&C&D select Y<= ‘1’ when “0001”|“0010” |“1101” |“1110”, ‘0’ when others;

e) with A&B&C&D select Y<= ‘1’ when “0100”|“0111” |“1000” |“1011”, ‘0’ when others;

f) with A&B&C&D select Y<= ‘1’ when “0101”|“0110” |“1001” |“1010”, ‘0’ when others;

Resolución:

with A&B&C&D select

Y<= ‘1’ when “1100”|“1111” |“1001” |“1010”,

‘0’ when others;

✅ Problema #4 (10%). El siguiente es un Sistema Digital que tiene las señales ‘A’,’ B’, ‘C’ y ‘D’ como entradas de un bit; por otro lado, la señal ‘Y’ es una salida de un bit tal como se muestra en la siguiente imagen:

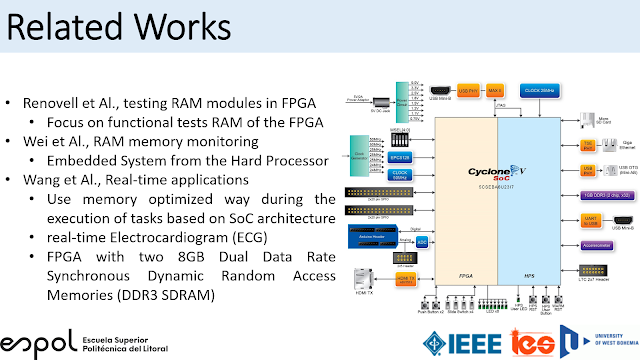

- Read related topics:

- ✅ Video de #VHDL (Ejemplo 2 - secuencialidad)

- ✅ Video de #VHDL (Ejemplo 1 - concurrencia)

- ✅ 2021 PAE: 1ra Lección C2

- ✅ 2021 PAE: 1ra Lección C1

- ✅ 2020 PAO1: Examen 1ra Evaluación

- ✅ 2020 PAO1: 1ra Lección C1-3 B

- ✅ 2020 PAO1: 1ra Lección C1-3A

- ✅ 2018 1T: Examen 1ra Evaluación

- ✅ 2017 2T: Lección 2da Evaluación

- ✅ 2017 2T: Lección 1ra Evaluación

- ✅ 2017 1T: Lección 2da Evaluación

- ✅ 2017 1T: Examen 1ra Evaluación

- ✅ 2017 1T: Lección 1ra Evaluación

- ✅ 2017 1T: Ejercicios 1ra Evaluación

Comentarios

Publicar un comentario