▷ DETECTOR EFICIENTE DE SECUENCIA NUMÉRICA EN #VHDL CON #FPGA #DE0_NANO

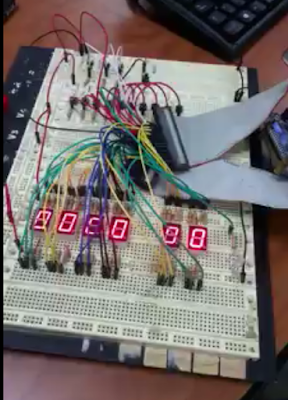

⭐⭐⭐⭐⭐ DETECTOR EFICIENTE DE SECUENCIA NUMÉRICA EN #VHDL CON #FPGA #DE0_NANO ➡️ #DigitalSystems #DigitalElectronic #DigitalCircuits #HDL #VHDL #FPGA ⭐ https://github.com/vasanza/MSI-VHDL ✅ Por: Irving Valeriano ( ivaleria@espol.edu.ec ) Soria Cortez ( vasoria@espol.edu.ec ) ✅ DESCRIPCIÓN: En el siguiente proyecto se pretende desarrollar un sistema eficiente para la búsqueda del número que más se repite dentro de una secuencia de números ingresados por el usuario. El programa constará de un teclado por el cual se ingresarán los números que el usuario decida, para lo cual el mismo deberá presionar la tecla de Ingreso de datos y una vez que culmine de ingresarlos deberá presionar la botonera de Fin de ingreso, después de lo cual el sistema queda a la espera de la botonera Start con la cual procederá a realizar la selección del número que más se repite. Una vez que se ha seleccionado el número se usaran displays en los cuales se mostrará el número que más veces se repite j...