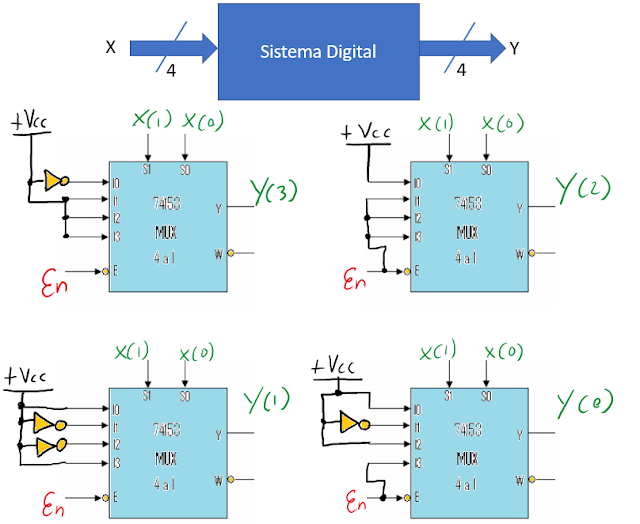

▷ SOLUCIÓN LECCIÓN SISTEMAS DIGITALES 1, 2do Parcial (2020 PAO 1) C5 A

⭐⭐⭐⭐⭐ SOLUCIÓN LECCIÓN SISTEMAS DIGITALES 1, 2do Parcial (2020 PAO 1) C5 A from Victor Asanza ➡️ #DigitalSystems #DigitalElectronic #DigitalCircuits #HDL #VHDL #FPGA ⭐ https://github.com/vasanza/MSI-VHDL El siguiente código #VHDL describe el funcionamiento de un flip-flop “XY” (FF-XY). Para realizar una conversión exitosa de un flip-flop “JK” (FF-JK) a un FF-XY, determinar cuáles de las siguientes expresiones booleanas describen correctamente el funcionamiento de las señales “J” y “K”: ✅ a) j <= not(x) or not (y); ✅ b) j <= not(x) or y; ✅ c) j <= x or not(y); ✅ d) j <= x or y; ✅ e) k <= not(x) or not (y); ✅ f) k <= not(x) or y; ✅ g) k <= x or not(y); ✅ h) k <= x or y; Read related topics : ✅ 2020 PAO1: 2da Lección C4 B ✅ 2020 PAO1: 2da Lección C4 A ✅ 2018 1T: Examen 3ra Evaluación ✅ 2018 1T: Examen 2da Evaluación ✅ 2018 1T: Lección 2da Evaluación ✅ 2017 2T...