▷ SOLUCIÓN EXAMEN SISTEMAS DIGITALES 2, 2do Parcial (2022PAO2)

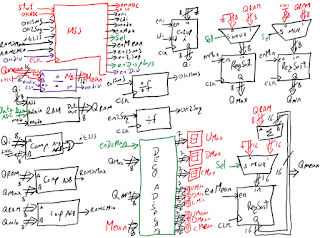

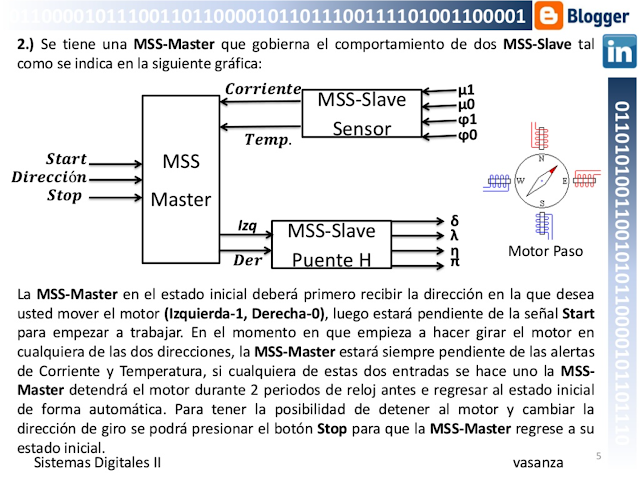

⭐⭐⭐⭐⭐ SOLUCIÓN EXAMEN SISTEMAS DIGITALES 2, 2do Parcial (2022PAO2) ➡️ #DigitalSystems #DigitalElectronic #DigitalCircuits #HDL #VHDL #FPGA ⭐ https://github.com/vasanza/MSI-VHDL Repositorio con los archivos VHDL de la pregunta: https://github.com/vasanza/DigitalSystems/tree/2022PAO2/2022_PAO2_2P_Examen La siguiente partición funcional que incluye una Maquina Secuencial Sincrónica (MSS), debe realizar una búsqueda del valor máximo y el valor mínimo multiplicado entre dos memorias RAM de 255 valores (Asuma que las memorias RAM1 y RAM2 ya están llenas con valores aleatorios entre 0 a 15). Para empezar a realizar la búsqueda, la MSS deberá recibir un valor de uno en la señal de entrada “Start” (Start = 1) y la MSS indicará por medio de la señal de salida “Fin” el momento en que termine de realizar la búsqueda (Fin = 1). Si se quiere regresar al estado inicial para realizar una nueva búsqueda, la MSS deberá recibir un valor de uno en la señal de entrada “OK” (OK = 1). El sistema d...