▷ SOLUCIÓN EVALUACIÓN SISTEMAS DIGITALES 2, 2do Parcial (2021 PAO 2)

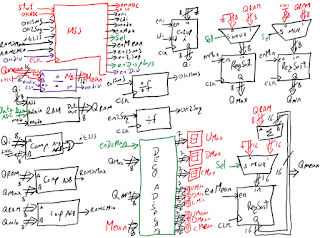

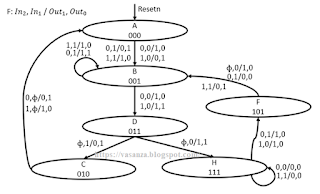

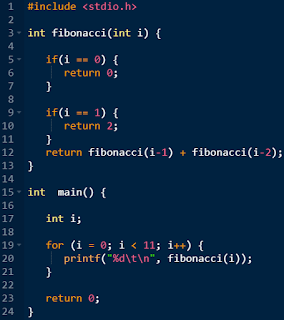

⭐⭐⭐⭐⭐ SOLUCIÓN EVALUACIÓN SISTEMAS DIGITALES 2, 2do Parcial (2021 PAO 2) from Victor Asanza ➡️ #DigitalSystems #DigitalElectronic #DigitalCircuits #HDL #VHDL #FPGA ⭐ https://github.com/vasanza/MSI-VHDL La siguiente partición funcional que incluye una Maquina Secuencial Sincrónica (MSS), debe realizar una búsqueda del valor máximo y el valor mínimo de 255 valores que deberán ser ingresados en una memoria RAM. El ingreso de estos valores de 8 bits se debe realizar de uno a uno empleando la señal WriteData (se recomienda usar anti-rebote), estos valores deberán ser ingresados por el puerto “Data”, mientras esto ocurre la salida “WritingData” permanece activa. Este proceso finaliza luego de ingresar 255 valores en la memoria RAM. Luego la MSS deberá realizar la búsqueda del número más alto ingresado y del menor ingresado, para lo cual se recomienda usar el contador_up “i” en el proceso de búsqueda de ambos valores de forma simultánea. Se pide: a) Complet...