▷ SOLUCIÓN EVALUACIÓN SISTEMAS DIGITALES 1, 1er Parcial (2021 PAO1)

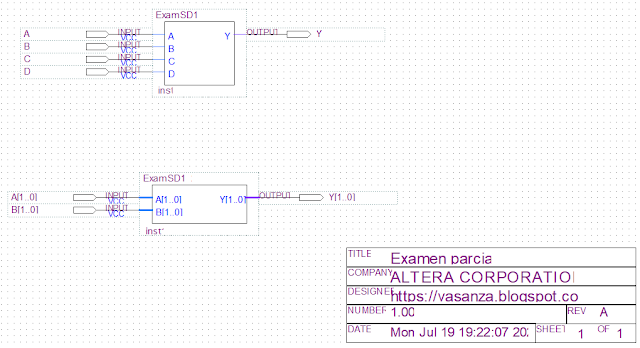

⭐⭐⭐⭐⭐ SOLUCIÓN EVALUACIÓN SISTEMAS DIGITALES 1, 1er Parcial (2021 PAO1) from Victor Asanza ➡️ #DigitalSystems #DigitalElectronic #DigitalCircuits #HDL #VHDL #FPGA ⭐ https://github.com/vasanza/MSI-VHDL ✅ Problema #1 (x%) . El siguiente es un Sistema Digital que tiene las señales ‘A’,’ B’, ‘C’ y ‘D’ como entradas de un bit; por otro lado, la señal ‘Y’ es una salida de un bit tal como se muestra en la siguiente imagen: El comportamiento de la señal de salida ‘Y’ en función de las señales de entrada, es descrito con el siguiente código VHDL: ⭐ Código GitHub: https://github.com/vasanza/MSI-VHDL/blob/2021PAO1/ExamenParcial/ExamSD1_1.vhd Realizar los siguientes desarrollos: a) Usando mapas de karnaught y agrupamiento de minterms (SOP), simplificar la expresión booleana hasta obtener su minima expresión (x/2 %). b) Utilizando puertas lógicas, graficar el circuito que represente a la ecuación simplificada en el literal anterior (x/2 %). Resolución: a) b) ✅ ...