▷ SOLUCIÓN LECCIÓN SISTEMAS DIGITALES 2, 1er Parcial (2021PAO2) C2

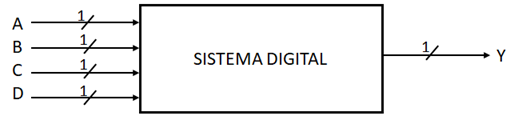

⭐⭐⭐⭐⭐ SOLUCIÓN LECCIÓN SISTEMAS DIGITALES 2, 1er Parcial (2021PAO2) C2 from Victor Asanza ➡️ #DigitalSystems #DigitalElectronic #DigitalCircuits #HDL #VHDL #FPGA ⭐ https://github.com/vasanza/MSI-VHDL El siguiente circuito implementado con memoria ROM representa la implementación de una Maquina Secuencial Sincrónica (MSS). La memoria ROM Funciona como el circuito decodificador de estados siguientes y salidas, mientras que los Flip-Flop tipo D (FF-D) son la memoria de estado. Tener en mente las siguientes consideraciones de la memoria EPROM: La palabra de código de programa de la EPROM M2732A debe tener siempre ocho bits. Entonces los tres bits que faltan para completar la palabra se dejan en 1 ya que una EPROM sin programar tiene todas las salidas en 1. Las instrucciones almacenadas en la EPROM son: Presentar: ✅ Los mapas de Karnaugh que describen los decodificadores de estados siguientes y salidas. Utilizando la siguiente asignación de códigos de estado y f...