▷ SISTEMA MULTIPLICADOR DE MATRICES 3X4 y 4X3 EN #VHDL CON FPGA #DE0_NANO

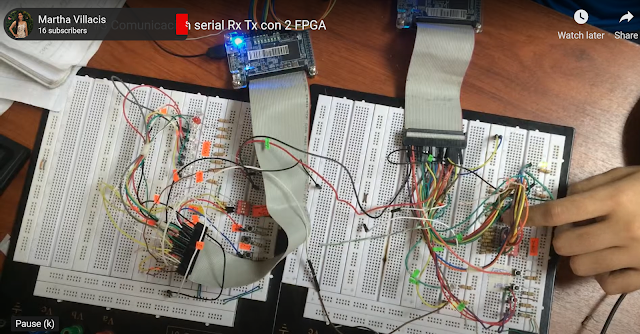

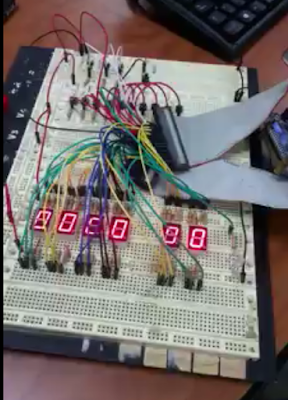

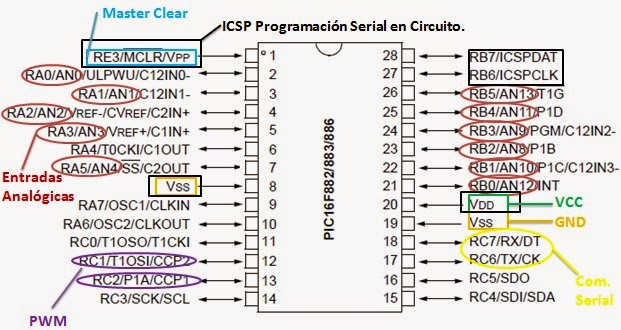

⭐⭐⭐⭐⭐ SISTEMA MULTIPLICADOR DE MATRICES 3X4 y 4X3 EN VHDL CON FPGA DE0-NANO ➡️ #DigitalSystems #DigitalElectronic #DigitalCircuits #HDL #VHDL #FPGA ⭐ https://github.com/vasanza/MSI-VHDL Por: Kerly Ochoa Erazo: kermaoch@espol.edu.ec Christian Sacarelo: csacarel@espol.edu.ec Descripción: Se trata de ingresar de manera serial 2 matrices de 3x4 y 4x3, luego de esto proceder a multiplicarlas y mostrar su resultado de manera serial. LINK VIDEO: https://www.facebook.com/christian.sacarelo/videos/10208017464453689/ Leer temas relacionados ✅ 2020 Paper: Behavioral Signal Processing with Machine Learning based on #FPGA ✅ 2020 Paper: Implementation of a Classification System of #EEG Signals Based on #FPGA ✅ 2020 Paper: Monitoring of system memory usage embedded in #FPGA ✅ 2019: Artificial Neural Network based #EMG recognition for gesture communication (#InnovateFPGA) ✅ Projects Digital Systems Design #FPGA ➡️ Example: Determi...