▷ SOLUCIÓN EVALUACIÓN SISTEMAS EMBEBIDOS, 2do Parcial (2020 PAO 2)

- ➡️ #EmbeddedSystems #ARM #Python #CProgrammingLanguage #AVR #Esp32 #Espressif #IoT #CyberPhysicalSystem #SensorNetwork #WirelessSensorNetwork #Processor #Arduino #RaspberryPi #FreeRTOS

- ⭐ https://github.com/vasanza/EmbeddedSystems

- ✅ Problema #1: ¿Cuáles de las siguientes afirmaciones referentes a los sistemas Multiprocessor son ciertas?

- a) En este modelo, hay una memoria compartida común (grande) para todos los procesadores.

- b) Diferentes núcleos ejecutan diferentes hilos (instrucciones múltiples), operando en diferentes partes de la memoria (datos múltiples).

- c) Todos los núcleos comparten la misma memoria.

- d) Cada procesador tiene su propia (pequeña) memoria local, y su contenido no se replica en ningún otro lugar.

- ✅ Problema #2: ¿Cuáles de las siguientes afirmaciones referentes a los sistemas Multicore son ciertas?

- a) En este modelo, hay una memoria compartida común (grande) para todos los procesadores.

- b) Diferentes núcleos ejecutan diferentes hilos (instrucciones múltiples), operando en diferentes partes de la memoria (datos múltiples).

- c) Todos los núcleos comparten la misma memoria.

- d) Cada procesador tiene su propia (pequeña) memoria local, y su contenido no se replica en ningún otro lugar.

- ✅ Problema #3: ¿Cuáles de las siguientes afirmaciones son desventajas de usar Real Time Operating System (RTOS)?

- a) Ninguna de las opciones

- b) Requieren más memoria RAM que un Sistema sin RTOS

- c) Desarrollar software para un RTOS requiere de experiencia y planeamiento cuidadoso

- d) Una aplicación típica es alrededor de 15 K en tamaño, de las cuales el sistema operativo base es de aproximadamente 400 bytes.

- e) Controlar acceso a recursos utilizados por más de una tarea

- f) Todo byte debe ir acompañado de un bit de reconocimiento ACK

- g) Un RTOS permite organizar tareas de manera lógica y sencilla, asignando una prioridad a cada una de ellas

- ✅ Problema #4: ¿Cuáles de las siguientes afirmaciones son ventajas de usar Real Time Operating System (RTOS)?

- a) Asegura la dependencia entre tareas

- b) Refuerza conceptos de modularizarían

- c) Incrementa el tiempo de desarrollo

- d) El código implementado dentro de una rutina de atención a interrupción debe ocupar pocos ciclos de procesador.

- e) Facilita la extensibilidad y verificación del diseño

- f) Provee de métodos seguros de Comunicaciones entre tareas

- ✅ Problema #5: ¿Cuáles de las siguientes afirmaciones son los requisitos para un Real Time Operating System (RTOS)?

- a) Control del usuario

- b) Insensibilidad

- c) Tolerancia a los fallos

- d) Elevada potencia en la alimentación de energía

- e) Determinismo

- f) Sensibilidad

- g) Potente sistema de disipación de temperatura

- h) Fiabilidad

- i) Todas las anteriores

- j) Ninguna de las anteriores.

- ✅ Problema #6: ¿Cuáles de las siguientes afirmaciones son características de las colas para comunicar datos entre tareas en un Real Time Operating System (RTOS)?

- a) El sistema determinista nos permite predecir el comportamiento del programador del sistema RTOs, garantizando así que se cumplan los requisitos de tiempo real.

- b) El sistema debe atender los eventos dentro de un tiempo estrictamente definido.

- c) Los semáforos binarios es la mejor opción para implementar la exclusión mutual simple y el Mutex son mejor una opción para implementar la sincronización (entre tareas o entre tareas y una interrupción).

- d) El programador en un RTOS proporciona un patrón de ejecución predecible o determinista, valioso para sistemas integrados en aplicaciones de tiempo real.

- e) El código implementado dentro de una rutina de atención a interrupción debe ocupar pocos ciclos de procesador.

- f) Ninguna de las anteriores.

- ✅ Problema #7: ¿Cuáles de las siguientes son razones por las cuales usar el TinyOS?

- a) Diseñado para trabajar con recursos limitados

- b) Reactive Concurrency

- c) Es flexible al ser independiente de la frontera entre hardware y software.

- d) Ideal para para funcionamiento continuo ya que permite la gestión de energía y ciclos de trabajo.

- e) Ninguna de las anteriores.

- ✅ Problema #8: ¿Cuáles de las siguientes son características del modelo de programación basado en componentes utilizado por el TinyOS?

- a) Ninguna de las opciones

- b) Una aplicación típica es alrededor de 15 K en tamaño, de las cuales el sistema operativo base es de aproximadamente 400 bytes

- c) Modelo de programación proporcionado por el idioma NESC

- d) Todo byte debe ir acompañado de un bit de reconocimiento ACK

- e) Encapsulan un conjunto específico de servicios mediante interfaces

- f) Entre un byte y el siguiente puede haber un tiempo ‘t’ de espera para que uno de los dispositivos realice las operaciones que corresponda

- g) Conjunto de componentes de sistemas reutilizables con un programador de tareas

- h) La genera un maestro y con ello reinicia el bus

- i) Ninguna de las anteriores.

- ✅ Problema #9: Seleccionar la opción que indica correctamente los nombres de la siguiente gráfica referente a la ejecución de una tarea de tiempo real, utilizar las siguientes opciones:

- a) 1- Tiempo de respuesta, 2- Activación, 3- Terminación, 4- Arranque, 5- Límite, 6- Ejecución de la tarea, 7- Plazo de ejecución

- b) 1- Plazo de ejecución, 2- Activación, 3- Terminación, 4- Arranque, 5- Límite, 6- Ejecución de la tarea, 7- Tiempo de respuesta

- c) 1- Tiempo de respuesta, 2- Activación, 3- Límite, 4- Arranque, 5- Terminación, 6- Ejecución de la tarea, 7- Plazo de ejecución

- d) 1- Tiempo de respuesta, 2- Arranque, 3- Terminación, 4- Activación, 5- Límite, 6- Ejecución de la tarea, 7- Plazo de ejecución

- e) 1- Tiempo de respuesta, 2- Activación, 3- Terminación, 4- Arranque, 5- Límite, 6- Plazo de ejecución, 7- Ejecución de la tarea

- f) 1- Ejecución de la tarea, 2- Activación, 3- Terminación, 4- Arranque, 5- Límite, 6- Tiempo de respuesta, 7- Plazo de ejecución

- ✅ Problema #10: Seleccionar la opción que indica correctamente los nombres de la siguiente gráfica referente al Kernel del RTOS que facilita a los distintos programas acceso seguro al hardware:

- a) 1- El momento en que se produce la interrupción; 2- El instante en que el Kernel ejecuta un tick interrupt para seleccionar la siguiente tarea; 3- La nueva tarea seleccionada se ejecuta cuando se completa la interrupción.

- b) 1- El momento en que se produce la interrupción; 2- Entre un byte y el siguiente puede haber un tiempo ‘t’ de espera para que uno de los dispositivos realice las operaciones que corresponda; 3- La nueva tarea seleccionada se ejecuta cuando se completa la interrupción.

- c) 1- El momento en que se produce la interrupción; 2- El instante en que el Kernel ejecuta un tick interrupt para seleccionar la siguiente tarea; 3- El código implementado dentro de una rutina de atención a interrupción debe ocupar pocos ciclos de procesador.

- d) 1- La nueva tarea seleccionada se ejecuta cuando se completa la interrupción; 2- El instante en que el Kernel ejecuta un tick interrupt para seleccionar la siguiente tarea; 3- La nueva tarea seleccionada se ejecuta cuando se completa la interrupción.

- e) 1- El instante en que el Kernel ejecuta un tick interrupt para seleccionar la siguiente tarea; 2- El momento en que se produce la interrupción; 3- La nueva tarea seleccionada se ejecuta cuando se completa la interrupción.

- f) 1- El momento en que se produce la interrupción; 2- La nueva tarea seleccionada se ejecuta cuando se completa la interrupción; 3- El instante en que el Kernel ejecuta un tick interrupt para seleccionar la siguiente tarea.

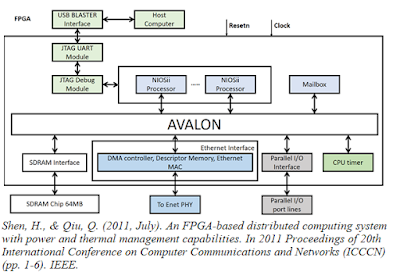

- ✅ Problema #11a: Shen et Al., escribió el paper titulado “An FPGA-based Distributed Computing System with Power and Thermal Management Capabilities” en donde desarrolla una plataforma computacional distribuida compuesta de múltiples FPGAs conectadas via Ethernet y cada FPGA está configurada como un sistema multi-core. Los núcleos en el mismo FPGA se comunican a través de la memoria compartida, mientras que diferentes FPGA se comunican a través de enlaces Ethernet. Las FPGAs están en las tarjetas de desarrollo Altera Nios II Embedded Evaluation Kit (NEEK), la edición de Altera NEEK Cyclone III tiene un Cyclone III EP3C25F324 FPGA con 25,000 elementos lógicos y 594 Kbits Memoria incorporada, 32 MB DDR SDRAM, 1 MB SRAM, 16 MB Flash Intel P30 / P33, pantalla táctil de 800 X 480, Ethernet 10/100 Mbps, y conector PS2 y RS-232. Desarrollar el diagrama de bloques basado en el NIOSii processor que considere debió utilizar Shen et Al. en cada una de las FPGA, basado en las siguientes especificaciones:

- El JTAG UART proporciona la interfaz de puerto de depuración.

- Se incluye un temporizador de alta resolución para medir el tiempo de ejecución del programa.

- La E / S paralela (PIO) proporciona control y monitoreo al reloj.

- Una o varias memorias compartidas están conectadas a cada subsistema Nios II. Estas memorias compartidas se configuran como Mailbox de hardware para las comunicaciones entre los procesadores en el mismo FPGA.

- Entre todos los subsistemas Nios II en el mismo FPGA, hay uno que tiene un módulo de interfaz Ethernet.

- El módulo de interfaz Ethernet consta de un controlador Direct Memory Access (DMA), una memoria de descriptor y el MAC de Ethernet.

- El subsistema Nios II que tiene la interfaz Ethernet que actúa como una puerta de enlace para las comunicaciones entre FPGA en el sistema informático distribuido.

- Todos los periféricos están conectados al procesador Nios II a través de la interfaz mapeada en memoria de Avalon.

- La interfaz de transmisión de Avalon se utiliza para conectar el DMA al controlador Ethernet.

- Se pide:

- a) Dibujar el Data Flow Diagram (DFD) de cada uno de los componentes del sistema descrito, incluir las entidades externas, procesos que usted considere necesarios en cada sistema embebido, almacenamiento y flujo de datos.

- b) Proponer la realización del sistema descrito, pero ahora con un sistema embebido basado en procesador ARM (Raspberry Pi).

- c) Indicar cuál de las siguientes gráficas corresponde al Diseño SoPC en las FPGAs propuesto por los autores:

- Referencia:

- Shen, H., & Qiu, Q. (2011, July). An FPGA-based distributed computing system with power and thermal management capabilities. In 2011 Proceedings of 20th International Conference on Computer Communications and Networks (ICCCN) (pp. 1-6). IEEE.

- ✅ Problema #11b: Belwafi et Al., escribió el paper titulado “A Hardware/Software Prototype of EEG-based BCI System for Home Device Control” en donde desarrolla un Brain Computer Interface (BCI) basado en FPGA. La arquitectura se basa en la tecnología FPGA construida con el entorno Altera y herramientas integradas dedicadas como: Qsys para los componentes de diseño de hardware y Eclipse para el desarrollo de software integrado. El sistema integrado propuesto que incluye:

- La versión más rápida de Nios-II, caché de datos con un tamaño de 64 Kbytes y caché de instrucciones de 4 Kbytes.

- Un temporizador para medir el tiempo de ejecución, con contador de 32 bits y un tiempo de espera de 10 microsegundos.

- JTAG-UART para establecer comunicación entre Eclipse y la placa Stratix-IV.

- Memoria DDR2 con 1 GB de tamaño.

- DMA (Acceso directo a memoria) transfiere datos de la manera más eficiente posible, leyendo y escribiendo datos en el espacio máximo asignado por la fuente o el destino.

- Memoria en chip con un tamaño de 4 KB para sincronizar la transferencia de datos entre el origen y el destino a través de la interfaz DMA.

- PLL para la generación de reloj y el diseño del sistema de sincronización.

- Se pide:

- a) Dibujar el Data Flow Diagram (DFD) de cada uno de los componentes del sistema descrito, incluir las entidades externas, procesos que usted considere necesarios en cada sistema embebido, almacenamiento y flujo de datos.

- b) Proponer la realización del sistema descrito, pero ahora con un sistema embebido basado en procesador ARM (Raspberry Pi).

- c) Indicar cuál de las siguientes gráficas corresponde al Diseño SoPC en las FPGAs propuesto por los autores:

- Referencia:

- Belwafi, K., Ghaffari, F., Djemal, R., & Romain, O. (2017). A hardware/software prototype of EEG-based BCI system for home device control. Journal of Signal

- ✅ Problema #11c: Lin et Al., escribió el paper titulado “Design of servo control system based on Nios soft core CPU” en donde desarrolla un módulo de servocontrol. La arquitectura se basa en la tecnología FPGA construida con el entorno Altera y herramientas integradas dedicadas como: Qsys para los componentes de diseño de hardware y Eclipse para el desarrollo de software integrado. El sistema integrado propuesto que incluye:

- El procesador central es EP1C12Q240, una serie de chips FPGA Cyclone producidos por Altera Company. Principalmente completa la recepción de la entrada digital y la corrección de errores del módulo SDC del módulo de detección de posición, recibe las instrucciones de control de posición y velocidad de la computadora host, realiza la iteración de interpolación, completa el control PID de posición y velocidad, cambia el control de entrada y salida, y se comunica con la computadora host.

- Módulo SDC, que utiliza el convertidor digital de doble canal selsyn / resolutor M2S44RDC / SDC para completar la extracción de posición y la conversión digital.

- Módulo de comunicación de bus SPI, que utiliza un módulo de bus SPI personalizado dentro del FPGA para comunicarse con la computadora host, para completar la interacción de información con la computadora host.

- SRAM: se adopta el chip SRAM asíncrono de alta velocidad ISSI IS61LV25616AL con capacidad de 256K * 16Bit. La señal de Word Enabler es independiente y puede operar en cada byte.

- SDRAM: se adopta K4S32323232F de la compañía SAMSUNG, y su capacidad es de 2M * 32Bit.

- FLASH: se adopta el Am29LV160D de AMD con una capacidad de 1M * 16Bit.

- Módulo de control del bus: el controlador emite la señal del bus de datos. El chip de control de bus SN74LVCC3245 se utiliza para el control de bus, que tiene las funciones de control de dirección, aislamiento de señal y amplificación.

- Interfaz AS: el dispositivo EPCS se programa directamente a través de la interfaz AS.

- Interfaz JTAG: puede descargar la configuración a FPGA, programa de depuración, programa para Flash y programa para dispositivo EPCS.

- Se pide:

- a) Dibujar el Data Flow Diagram (DFD) de cada uno de los componentes del sistema descrito, incluir las entidades externas, procesos que usted considere necesarios en cada sistema embebido, almacenamiento y flujo de datos.

- b) Proponer la realización del sistema descrito, pero ahora con un sistema embebido basado en procesador ARM (Raspberry Pi).

- c) Indicar cuál de las siguientes gráficas corresponde al Diseño SoPC en las FPGAs propuesto por los autores:

- Referencia:

- Lin, Y. (2019, March). Design of servo control system based on Nios soft core CPU. In IOP Conference Series: Earth and Environmental Science (Vol. 242, No. 3, p. 032004). IOP Publishing.

- ✅ Problema #11d: Bilendo et Al., escribió el paper titulado “Hardware Design of a Flight Control Computer System based on Multi-core Digital Signal Processor and Field Programmable Gate Array” en donde desarrolla un sistema de hardware basado en FPGA para mejorar la potencia de procesamiento y optimizar la relación rendimiento / tamaño para un sistema de control de vuelo. La FPGA juega un papel muy importante en el sistema, ya que la CPU Soft-Core está construida dentro de la FPGA y todos los componentes del sistema están conectados a la CPU Soft-Core a través de la FPGA. El procesador del sistema digital (DSP) también desempeña un papel importante al proporcionar a la placa su potencia de procesamiento secuencial, mientras que el FPGA realiza funciones de interfaz paralela y de bajo nivel para componentes externos como el GPS y la IMU. El DSP es TMS320C6678 basado en múltiples núcleos con muchas ventajas para las capacidades de procesamiento, y se comunica con el FPGA a través del puerto UART al bus de datos Avalon. La placa del sensor está representada por ADIS16350, que es un giroscopio y acelerómetro Tri Axis, que es básicamente el conjunto completo de IMU. Esto se incrementa con sensores de presión absoluta y diferencial y un módulo OEM μBlox GPS. El sistema integrado en el FPGA emplea Nios-II, que es un sistema de procesador equivalente a un microcontrolador o “computadora en un chip” que incluye un procesador y una combinación de periféricos y memoria en un solo chip. La idea es combinar un sistema basado en microcontrolador con el FPGA para superar las limitaciones de la mayoría de los FCS actualmente en el mercado y mejorar el rendimiento. El sistema integra los siguientes componentes:

- Avalon Data Bus and Memory: La interfaz Avalon es una interfaz síncrona definida por un conjunto de tipos de señal con funciones para soportar la transferencia de datos. Hay dos tipos de puerto de interfaz Avalon, el puerto maestro Avalon y el puerto esclavo Avalon. El puerto maestro de Avalon inicia la transferencia y el puerto esclavo de Avalon responde a las solicitudes de transferencia. El Avalon Bus se comunica con la memoria del sistema (memoria en chip y SDRAM) para almacenar datos para el sistema.

- Universal Asynchronous Receiver/Transmitter: El UART con interfaz Avalon implementa un método para comunicar flujos de caracteres en serie entre un sistema integrado en un Intel FPGA y un dispositivo externo (en este caso, DSP Multi-Core y GPS). El núcleo implementa la sincronización del protocolo RS-232 y proporciona velocidad de transmisión ajustable, paridad, parada y bits de datos. El core UART proporciona una interfaz esclava Avalon Memory-Mapped (Avalon-MM) que permite que los periféricos maestros Avalon-MM (como un procesador Nios-II) se comuniquen con el núcleo simplemente leyendo y escribiendo el control y registros de datos.

- Serial Peripheral Interface: El SPI con la interfaz Avalon implementa el protocolo SPI y proporciona una interfaz Avalon Memory-Mapped (Avalon-MM) en el back-end. El núcleo SPI puede implementar el protocolo maestro o esclavo. El SPI es el protocolo de comunicación entre la FPGA y la IMU (ADIS16350).

- Counter and Pulse-Width Modulation: Se requiere una interfaz de modulación de ancho de pulso para controlar los servodrivers. Un servodriver se controla enviando un pulso cada cierta cantidad de ms (ejemplo: 20ms), o una cierta cantidad de Hz (ejemplo: 50Hz), al servo. La duración o el ancho del pulso determina el ángulo de salida del servo. Las especificaciones de los servos pueden variar entre fabricantes.

- JTAG- UART: El core JTAG UART con interfaz Avalon implementa un método para comunicar flujos de caracteres en serie entre una PC host y un sistema Platform Designer en un Intel FPGA. La interfaz visible para el usuario del núcleo JTAG UART consta de dos registros de 32 bits, datos y control, a los que se accede a través de un puerto esclavo Avalon. Un maestro Avalon, como un procesador Nios-II, accede a los registros para controlar el núcleo y transferir datos a través de la conexión JTAG. El núcleo opera en unidades de datos de 8 bits a la vez; ocho bits del registro de datos sirven como una carga útil de un carácter.

- Se pide:

- a) Dibujar el Data Flow Diagram (DFD) de cada uno de los componentes del sistema descrito, incluir las entidades externas, procesos que usted considere necesarios en cada sistema embebido, almacenamiento y flujo de datos.

- b) Proponer la realización del sistema descrito, pero ahora con un sistema embebido basado en procesador ARM (Raspberry Pi).

- c) Indicar cuál de las siguientes gráficas corresponde al Diseño SoPC en las FPGAs propuesto por los autores:

- Referencia:

- Bilendo, F., & Shouzhao, S. (2018). Hardware Design of a Flight Control Computer System based on Multi-core Digital Signal Processor and Field Programmable Gate Array.

- ✅ Problema #11e: M Li et Al., escribió el paper titulado “The Design of IP Core for LCD Controller Based on SOPC” en donde desarrolla un controlador para pantalla LCD utilizando un solo procesador NIOSii como se describe a continuación:

- El SOPC (System on Processor Chip) tiene una pantalla LCD que se conecta con el controlador LCD, la SDRAM se conecta con el controlador SDRAM y la comunicación de los dos controladores con el procesador NIOS II a través de la interfaz mapeada de memoria Avalon (Avalon-MM).

- El control de múltiples relojes generados por el mismo PLL puede generar relojes con diferentes frecuencias o fases. El componente Avalon ALTPLL agregado en Qsys puede generar cinco relojes diferentes como máximo, pero solo se necesitan dos salidas en este diseño. De acuerdo con el principio de funcionamiento de SDRAM, se sabe que los relojes que ingresan a la SDRAM y al controlador SDRAM deben tener la misma frecuencia y tener una cierta diferencia de fase para garantizar la lectura y escritura correcta de los datos.

- En este diseño, la entrada al controlador SDRAM y SDRAM es una señal de reloj bidireccional con una misma frecuencia de 100MHz y una diferencia de fase de 90 °. Y clk_100m2 exporta para el reloj de SDRAM, clk_50m es el reloj del sistema. Necesitamos configurar el sistema de procesador NIOS II, seleccionar y configurar los periféricos e IP, luego conectar los módulos periféricos, generar el sistema, diseñar el módulo de nivel superior en el software Quartus II, asignar los pines y compilarlos completamente, y descargar si se compila correctamente, el modelo del chip FPGA en esta placa de desarrollo es EP4CE10F17C8.

- Se pide:

- a) Dibujar el Data Flow Diagram (DFD) de cada uno de los componentes del sistema descrito, incluir las entidades externas, procesos que usted considere necesarios en cada sistema embebido, almacenamiento y flujo de datos.

- b) Proponer la realización del sistema descrito, pero ahora con un sistema embebido basado en procesador ARM (Raspberry Pi).

- c) Indicar cuál de las siguientes gráficas corresponde al Diseño SoPC en las FPGAs propuesto por los autores:

- Referencia:

- Li, M., Zhou, X., & Guo, Q. (2018). The Design of IP Core for LCD Controller Based on SOPC. In MATEC Web of Conferences (Vol. 232, p. 04074). EDP Sciences.

- ✅ 2020 Paper: Monitoring of system memory usage embedded in #FPGA

- ✅ 2020 PAO2: 2da Lección C6

- ✅ 2020 PAO2: 2da Lección C5

- ✅ 2020 PAO1: Examen de Mejoramiento

- ✅ 2020 PAO1: Examen 2da Evaluación

- ✅ 2020 PAO1: 3ra Lección C6

- ✅ 2020 PAO1: 2da Lección C5

- ✅ 2020 PAO1: Proyectos Propuestos

- ✅ End Device #Arduino #FreeRTOS

- ✅ End Device + Coordinator #Raspberry Pi #Python

- ✅ #Proteus #PCB Design

- ✅ #FPGA projects for Engineering Students

- ➡️ Sensor networks for #Agriculture

- ➡️ #PID control for DC motor

- ➡️ #PID control for angular position

- ➡️ Writing letters through eye movement using Machine Learning #ML

- ➡️ EyeTracker #Classification of subjects with Parkinson's using Machine Learning #ML

- ➡️ #EEG + #FlexSensor Medical Equipments - #HTMC

- ➡️ Digital synthesizer

- ➡️ Microcontroller Architecture #PIC #16F877A

- ➡️ Behavioral signal processing with Machine Learning #ML (Paper)

- ➡️ Phrases recognition with Machine Learning #ML (InnovateFPGA)

- ➡️ Alphabet letters recognition with #MachineLearning using #EMG signals (Paper)

- ➡️ #EMG signal #Classification with #MachineLearning (Paper)

- ➡️ Epileptic seizure prediction with #MachineLearning #ML

Comentarios

Publicar un comentario