▷ SOLUCIÓN EVALUACIÓN SISTEMAS DIGITALES 2, 2do Parcial (2020 PAO 2)

⭐⭐⭐⭐⭐ Maximum to minimum ordering of values in #RAM memory using #FPGA

- ➡️ #DigitalSystems #DigitalElectronic #DigitalCircuits #HDL #VHDL #FPGA

- ⭐ https://github.com/vasanza/MSI_VHDL

La siguiente partición funcional que incluye una Maquina Secuencial Sincrónica (MSS), debe realizar un ordenamiento de 255 valores de Mayor a Menor. El ingreso de estos valores de 8 bits se debe realizar de uno a uno, estos valores ingresan por el puerto “Data”, mientras se están ingresando los datos, la MSS pone en alto la salida “WritingData”, indicando que este proceso está siendo ejecutado y el mismo no terminará hasta completar los 255 valores. El ordenamiento de los números ingresados previamente se deberá realizar de mayor a menor, para lo cual se recomienda usar el contador_up “j” y el contador_up “i” en el proceso de búsqueda y comparación. Se pide:

a) Completar la partición funcional indicando el nombre del bloque amarillo con los respectivos nombres de las señales. Además, agregue cualquier componente que Ud. crea necesario para que el sistema funcione correctamente (justifique su respuesta). [3p]

b) Elaborar el ASM de la MSS, para que el circuito realiace el proceso de ingreso de valores y luego el de ordenamiento. Se recomienda presionar y soltar la entrada “Start” para dar el arranque al sistema completo. Asimismo, al finalizar la búsqueda, la MSS enciende la salida “Done” hasta que se presione y suelte nuevamente el botón “Start”[9p]

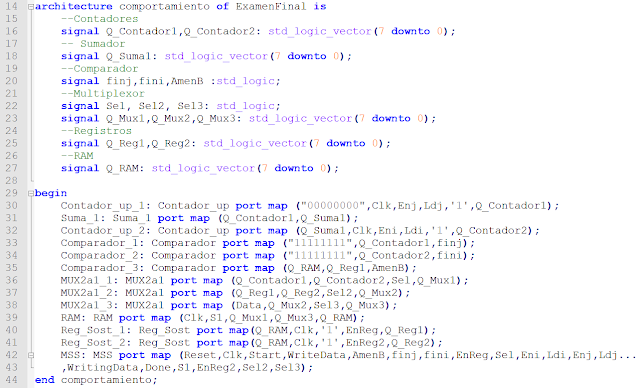

c) Finalmente, realizar el código VHDL del sistema completo con portMap, completando el nombre y funcionamiento del bloque faltante, nombres de señales y tamaño de buses. Asuma que los elementos que están en la partición funcional (incluido el de color amarillo) ya existen en la misma carpeta del proyecto [8p]

- Read related topics:

- ✅ 2020 PAO2: 2da Lección C4

- ✅ 2018 2T: Examen 3ra Evaluación

- ✅ 2018 2T: Examen 2da Evaluación

- ✅ 2018 2T: Lección 2da Evaluación

- ✅ 2018 1T: Examen 3ra Evaluación

- ✅ 2018 1T: Examen 2da Evaluación

- ✅ 2017 2T: Lección 2da Evaluación

- ✅ 2017 1T: Examen 2da Evaluación

- ✅ 2017 1T: Lección 2da Evaluación

- ✅ 2017 1T: Taller 2da Evaluación

- ✅ 2016 2T: Lección 2da Evaluación

- ✅ 2016 2T: Ejercicios 2da Evaluación

- ➡️ Example: Determinant of a matrix

- ➡️ Example: Numeric Sequence Detector

- ➡️ Example: Efficient Number Sequence Detector

- ➡️ Example: set operations

- ➡️ Example: communication and checksum validation

- ➡️ Example: Sum of Products Karnaugh Map

- ➡️ Example: Multiplying 3x4 matrix by 4x3 matrix

- ➡️ Example: Consecutive 1's Counter

- ➡️ Example: Numeric Sequence Counter

- ➡️ Example: Serial communication receiver

- ➡️ Example: billing system for telephone booths

- ➡️ Example: Temperature Conditioner

- ➡️ Example: Access control system (2)

- ➡️ Example: Access control system (1)

Comentarios

Publicar un comentario