▷ SISTEMA DE COMUNICACIÓN CON VALIDACIÓN CHECKSUM EN VHDL CON FPGA DE-NANO

SISTEMA DE COMUNICACIÓN CON VALIDACIÓN CHECKSUM EN VHDL CON FPGA DE-NANO

- ➡️ #DigitalSystems #DigitalElectronic #DigitalCircuits #HDL #VHDL #FPGA

- ⭐ https://github.com/vasanza/MSI-VHDL

Realizar el diseño de un SISTEMA DE COMUNICACIÓN CON VALIDACIÓN CHECKSUM. El sistema está conformado por un transmisor que envía datos bajo un protocolo establecido hacia módulos receptores que validarán la trama recibida.

Protocolo de comunicación:

Byte de Inicio: 0X24

Byte ID de Equipo: 0X01 ó 0X0A ó XA1

Byte de Data: 0X00 – 0XFF

Byte Checksum: XOR

SEÑALES TX

PaqueteOut.- esta señal de 8 bits envía cada uno de los paquetes de la trama byte a byte, es decir envía de forma ordenada primero Byte de Inicio, Byte de ID, Byte de data y finalmente Byte de CheckSum.

SincTx.-Esta señal sirve de sincronía para indicar al equipo receptor que existe un dato listo para ser leído.

StartTx.-Señal para empezar a enviar los datos.

StopTx.-Señal para detener el envío de datos.

IDRx.-El Byte de ID será leído constantemente antes de enviar los datos, de esa forma puede enviar la trama a diferentes equipos.

SEÑALES RX

PaqueteIn.- esta señal de 8 bits recibe cada uno de los paquetes de la trama byte a byte, es decir recibe de forma ordenada primero Byte de Inicio, Byte de ID, Byte de data y finalmente Byte de CheckSum.

SincRx.-Esta señal sirve de sincronía para indicar al equipo receptor que existe un dato listo para ser leído.

StartRx.-Señal que empezar a recibir los datos.

StopTx.-Señal para detener la recepción de datos.

IDRx.-El byte de ID es cargado inicialmente antes de presionar start de tal forma que el ID del equipo de recepción se compara con el ID recibido.

CÓDIGO VHDL

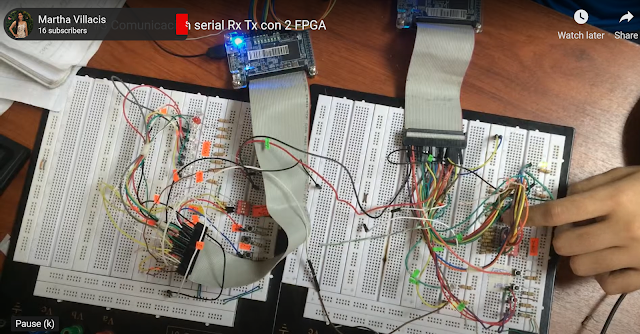

VIDEO LINK

Leer temas relacionados

- 2021PAO2: Lección 2da Evaluación C6

- 2021PAO2: Examen 1ra Evaluación

- 2021PAO2: Lección 1ra Evaluación C2

- 2021 PAO1: Example, Max to Min ordering values in RAM memory

- 2021 PAO1: Example, Maximum number finder and repetition counter

- 2021 PAO1: Proyectos Propuestos

- 2020 PAO2: Examen 3ra Evaluación

- 2020 PAO2: Examen 2da Evaluación

- 2020 PAO2: Lección 2da Evaluación C4

- 2020 PAO2: Examen 1ra Evaluación

- 2020 PAO2: Lección 1ra Evaluación C1-2

- 2018 2T: Examen 3ra Evaluación

- 2018 2T: Examen 2da Evaluación

- 2018 2T: Lección 2da Evaluación

- 2018 2T: Examen 1ra Evaluación

- 2018 2T: Lección 1ra Evaluación

- 2018 1T: Examen 3ra Evaluación

- 2018 1T: Examen 2da Evaluación

- 2017 2T: Lección 2da Evaluación

- 2017 1T: Examen 2da Evaluación

- 2017 1T: Lección 2da Evaluación

- 2017 1T: Taller 2da Evaluación

- 2017 1T: Examen 1ra Evaluación

- 2016 2T: Lección 2da Evaluación

- 2016 2T: Ejercicios 2da Evaluación

- 2016 2T: Lección 1ra Evaluación (2)

- 2016 2T: Lección 1ra Evaluación (1)

- 2016 2T: Taller 1ra Evaluación

- 2016 2T: Ejercicios 1ra Evaluación (2)

- 2016 2T: Ejercicios 1ra Evaluación (1)

- Digital System Implementation (2)

- Digital System Implementation (1)

- Example: Determinant of a matrix

- Example: Numeric Sequence Detector

- Example: Efficient Number Sequence Detector

- Example: set operations

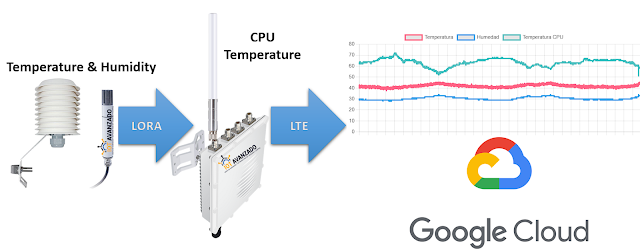

- Example: communication and checksum validation

- Example: Sum of Products Karnaugh Map

- Example: Multiplying 3x4 matrix by 4x3 matrix

- Example: Consecutive 1's Counter

- Example: Numeric Sequence Counter

- Example: Serial communication receiver

- Example: billing system for telephone booths

- Example: Temperature Conditioner

- Example: Access control system (2)

- Example: Access control system (1)

Comentarios

Publicar un comentario