▷ SOLUCIÓN EXAMEN SISTEMAS DIGITALES 2, 2do Parcial (2022PAO2)

- ➡️ #DigitalSystems #DigitalElectronic #DigitalCircuits #HDL #VHDL #FPGA

- ⭐ https://github.com/vasanza/MSI-VHDL

Repositorio con los archivos VHDL de la pregunta:

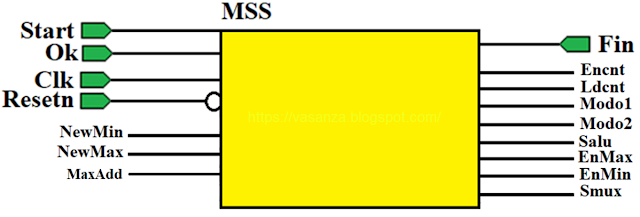

La siguiente partición funcional que incluye una Maquina Secuencial Sincrónica (MSS), debe realizar una búsqueda del valor máximo y el valor mínimo multiplicado entre dos memorias RAM de 255 valores (Asuma que las memorias RAM1 y RAM2 ya están llenas con valores aleatorios entre 0 a 15). Para empezar a realizar la búsqueda, la MSS deberá recibir un valor de uno en la señal de entrada “Start” (Start = 1) y la MSS indicará por medio de la señal de salida “Fin” el momento en que termine de realizar la búsqueda (Fin = 1). Si se quiere regresar al estado inicial para realizar una nueva búsqueda, la MSS deberá recibir un valor de uno en la señal de entrada “OK” (OK = 1). El sistema digital cuenta con una ALU que permite realizar operaciones de multiplicación y de suma (Q<=I0*I1 when Sel=0 else I0+I1 when Sel=1;), pero debido a que se requiere buscar el valor máximo y el valor mínimo multiplicado, se utilizará el Selector en modo multiplicación.

Se pide:

- a) Completar la partición funcional indicando todos los nombres de las señales de entrada y salida que le hacen falta al bloque MSS. Además, agregar el hardware necesario para que la MSS pueda detectar cuando ha terminado de recorrer todas las direcciones de memoria en RAM1 y RAM2. [x%]

- b) Elaborar el ASM de la MSS, para que el circuito realice la tarea solicitada. [x%]

- c) Presentar el código VHDL de la arquitectura completa del sistema digital, para lo cual deberá utilizar “port map” y asumirá que posee todos los códigos VHDL de los bloques MSI en la misma carpeta del proyecto. [x%]

Resolución:

a) Completar la partición funcional indicando todos los nombres de las señales de entrada y salida que le hacen falta al bloque MSS. Además, agregar el hardware necesario para que la MSS pueda detectar cuando ha terminado de recorrer todas las direcciones de memoria en RAM1 y RAM2. [x%]

b) Elaborar el ASM de la MSS, para que el circuito realice la tarea solicitada. [x%]

c) Presentar el código VHDL de la arquitectura completa del sistema digital, para lo cual deberá utilizar “port map” y asumirá que posee todos los códigos VHDL de los bloques MSI en la misma carpeta del proyecto. [x%]

Read related topics

- ⭐ 2021 Paper: Performance Comparison of Database Server based on #SoC #FPGA and #ARM Processor

- ⭐ 2021 Paper: #FPGA Based Meteorological Monitoring Station

- ⭐ 2020 Paper: Monitoring of system memory usage embedded in #FPGA

- ⭐ 2020 Paper: Implementation of a Classification System of #EEG Signals Based on #FPGA

- ⭐ 2019: Artificial Neural Network based #Accelerometer and #Gyroscope recognition for gesture communication (#InnovateFPGA)

- ✅ 2022PAO2: Examen 3ra Evaluación

- ✅ 2022PAO2: Examen 1ra Evaluación

- ✅ 2021PAO2: Examen 2da Evaluación

- ✅ 2021PAO2: Lección 2da Evaluación C6

- ✅ 2021PAO2: Examen 1ra Evaluación

- ✅ 2021PAO2: Lección 1ra Evaluación C2

- ✅ 2021 PAO1: Example, Max to Min ordering values in RAM memory

- ✅ 2021 PAO1: Example, Maximum number finder and repetition counter

- ✅ 2021 PAO1: Proyectos Propuestos

- ✅ 2020 PAO2: Examen 3ra Evaluación

- ✅ 2020 PAO2: Examen 2da Evaluación

- ✅ 2020 PAO2: Lección 2da Evaluación C4

- ✅ 2020 PAO2: Examen 1ra Evaluación

- ✅ 2020 PAO2: Lección 1ra Evaluación C1-2

- ✅ 2018 2T: Examen 3ra Evaluación

- ✅ 2018 2T: Examen 2da Evaluación

- ✅ 2018 2T: Lección 2da Evaluación

- ✅ 2018 2T: Examen 1ra Evaluación

- ✅ 2018 2T: Lección 1ra Evaluación

- ✅ 2018 1T: Examen 3ra Evaluación

- ✅ 2018 1T: Examen 2da Evaluación

- ✅ 2017 2T: Lección 2da Evaluación

- ✅ 2017 1T: Examen 2da Evaluación

- ✅ 2017 1T: Lección 2da Evaluación

- ✅ 2017 1T: Taller 2da Evaluación

- ✅ 2017 1T: Examen 1ra Evaluación

- ✅ 2016 2T: Lección 2da Evaluación

- ✅ 2016 2T: Ejercicios 2da Evaluación

- ✅ 2016 2T: Lección 1ra Evaluación (2)

- ✅ 2016 2T: Lección 1ra Evaluación (1)

- ✅ 2016 2T: Taller 1ra Evaluación

- ✅ 2016 2T: Ejercicios 1ra Evaluación (2)

- ✅ 2016 2T: Ejercicios 1ra Evaluación (1)

- ➡️ Example: Numeric Sequence Detector

- ➡️ Example: Efficient Number Sequence Detector

- ➡️ Example: set operations

- ➡️ Example: communication and checksum validation

- ➡️ Example: Sum of Products Karnaugh Map

- ➡️ Example: Multiplying 3x4 matrix by 4x3 matrix

- ➡️ Example: Consecutive 1's Counter

- ➡️ Example: Numeric Sequence Counter

- ➡️ Example: Serial communication receiver

- ➡️ Example: billing system for telephone booths

- ➡️ Example: Temperature Conditioner

- ➡️ Example: Access control system (2)

- ➡️ Example: Access control system (1)

Comentarios

Publicar un comentario